D. Richard Brown III Associate Professor Worcester Polytechnic Institute Electrical and Computer Engineering Department drb@ece.wpi.edu

24-November-2008

ECE4703 REAL-TIME DSP TMS320C6713 ARCHITECTURE OVERVIEW AND ASSEMBLY LANGUAGE PROGRAMMING

### Outline

- Letting CCS optimize your code for you

- Not good enough? Writing your own assembly language functions for the C6x

- Of Content of Conte

- Registers

- Functional units

- Pipelining

- Fetch/execute packets

## **Optimizing** Compiler

| Build Options 1                                                                                          | for Dotp4.pjt                                                                                               |                                                                                                                                                                                                                        | ? 🛛 |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| General Compi                                                                                            | er Linker Link Order                                                                                        | 1                                                                                                                                                                                                                      |     |

| -g -s -o3 -fr"C:\t                                                                                       | i\myprojects\Dotp4\Deb                                                                                      | ug" -d"CHIP_6713" -mv6710                                                                                                                                                                                              | <   |

| Category:<br>Basic<br>Advanced<br>Feedback<br>Files<br>Assembly<br>Parser<br>Preprocessor<br>Diagnostics | Basic<br>Target Version:<br>Generate Debug Info:<br>Opt Speed vs Size:<br>Opt Level:<br>Program Level Opt.: | C671x (-mv6710)<br>Full Symbolic Debug (-g)<br>Speed Most Critical (no -ms)<br>Speed Most Critical (no -ms)<br>Speed More Critical (-ms0)<br>Speed Critical(-ms1)<br>Size Critical (-ms2)<br>Size Most Critical (-ms3) | ×   |

|                                                                                                          |                                                                                                             |                                                                                                                                                                                                                        |     |

| Category:<br>Basic<br>Advanced<br>Feedback<br>Files<br>Assembly<br>Parser<br>Preprocessor<br>Diagnostics | Basic<br>Target Version:<br>Generate Debug Info:<br>Opt Speed vs Size:<br>Opt Level:<br>Program Level Opt.: | C671x (-mv6710)<br>Full Symbolic Debug (-g)<br>Speed Most Critical (no -ms)<br>File (-o3)<br>None<br>Register (-o0)<br>Local (-o1)<br>Function (-o2)<br>File (-o3)                                                     | •   |

Typical speed gains of 2x to 5x with compiler optimization.

# Assembly Language Programming on the TMS320C6713

- To achieve the best possible performance, sometimes you have to take matters into your own hands...

- Three options:

- I. Linear assembly (.sa)

- Compromise between effort and efficiency

- Typically more efficient than C

- Assembler takes care of details like assigning "functional units", registers, and parallelizing instructions

- 2. ASM statement in C code (.c)

- asm("assembly code")

- 3. <u>C-callable assembly function (.asm)</u>

- Full control of assigning functional units, registers, parallelization, and pipeline optimization

### C-Callable Assembly Language Functions

- Basic concepts:

- Arguments are passed in via registers A4, B4, A6, B6, ... in that order. All registers are 32-bit.

- Result returned in A4 also.

- Return address of calling code (program counter) is in B3.

Don't overwrite B3!

- Naming conventions:

- In C code: label

- In ASM code: \_\_label (note the leading underbar)

- Accessing global variables in ASM:

- .ref \_variablename

- A function prototype must also be included in your C code.

### Skeleton C-Callable ASM Function

; header comments ; passed in parameters in registers A4, B4, A6, ... in that order

| .def      | _myfunc          | ; allow calls from external  |

|-----------|------------------|------------------------------|

| ACONSTANT | .equ 100         | ; declare constants          |

| .ref      | _aglobalvariable | ; refer to a global variable |

| _myfunc: | NOP |    | ; instructions go here          |

|----------|-----|----|---------------------------------|

|          | В   | B3 | ; return (branch to addr B3)    |

|          |     |    | ; function output will be in A4 |

|          | NOP | 5  | ; pipeline flush                |

.end

## Example C-Callable Assembly Language Program (Chassaing) int fircasmfunc(short x[], short h[], int N)

| ;FIRCA | SMfunc.as | sm ASM functi | on called from C to implement FIR |

|--------|-----------|---------------|-----------------------------------|

| ;A4 =  | Samples a | address, B4 = | coeff address, A6 = filter order  |

| ;Delay | s organi: | zed as:x(n-(N | -1))x(n);coeff as h[0]h[N-1]      |

|        |           |               |                                   |

|        | .def      | _fircasmfun   | c                                 |

| _firca | smfunc:   |               | ;ASM function called from C       |

|        | MV        | A6,A1         | ;setup loop count                 |

|        | MPY       | A6,2,A6       | ;since dly buffer data as byte    |

|        | ZERO      | A8            | ; init A8 for accumulation        |

|        | ADD       | A6,B4,B4      | ;since coeff buffer data as byte  |

|        | SUB       | B4,1,B4       | ;B4=bottom coeff array h[N-1]     |

| loop:  |           |               | ;start of FIR loop                |

|        | LDH       | *A4++,A2      | ;A2=x[n-(N-1)+i] i=0,1,,N-1       |

|        | LDH       | *B4,B2        | ;B2=h[N-1-i] i=0,1,,N-1           |

|        | NOP       | 4             |                                   |

|        | MPY       | A2,B2,A6      | ;A6=x[n-(N-1)+i]*h[N-1-i]         |

|        | NOP       |               |                                   |

|        | ADD       | A6,A8,A8      | ;accumlate in A8                  |

|        | LDH       | *A4,A7        | ;A7=x[(n-(N-1)+i+1]update delays  |

|        | NOP       | 4             | using data move "up"              |

|        | STH       | A7,*-A4[1]    | ;>x[(n-(N-1)+i] update sample     |

|        | SUB       | A1,1,A1       | ;decrement loop count             |

| [A     | 1] B      | loop          | ;branch to loop if count # 0      |

|        | NOP       | 5             |                                   |

|        | MV        | A8,A4         | ;result returned in A4            |

|        | B<br>NOP  | B3<br>4       | ;return addr to calling routine   |

### Writing Efficient Assembly Language Programs for the C6x

- Need to become familiar with:

- Specific architecture, capabilities, and limitations of the C6x

- Registers

- Functional units

- Pipeline

- Parallelization

- •••

- Instruction set

- Different commands for single precision floating point, double precision floating point, and integer math

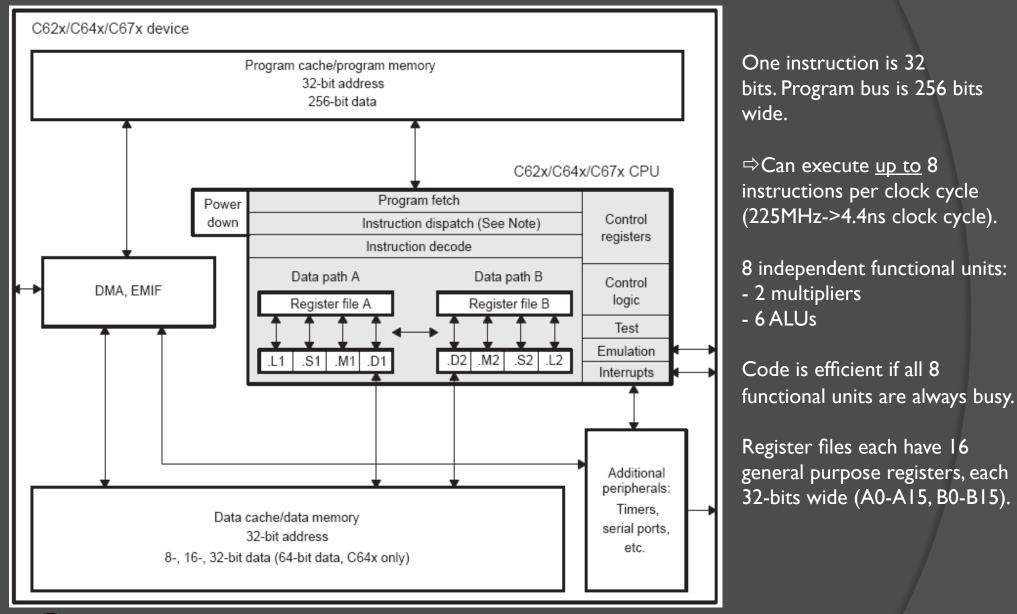

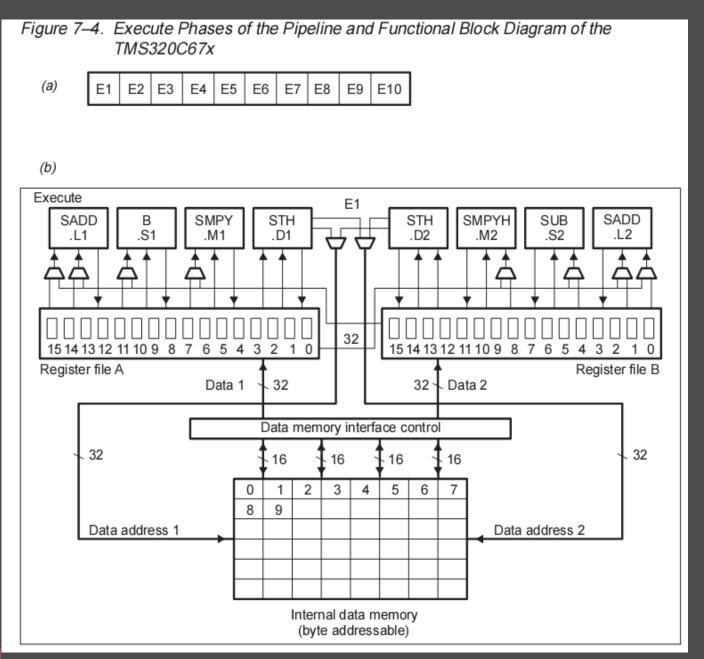

### TMS320C67x Block Diagram

### C6713 Data Paths and Functional Units

- Two data paths (A & B)

- Data path A

- Multiply operations (.MI)

- Logical and arithmetic operations (.L.I.)

- Branch, bit manipulation, and arithmetic operations (.51)

- Loading/storing and arithmetic operations (.DI)

- Data path B

- Multiply operations (.M2)

- Logical and arithmetic operations (.L2)

- Branch, bit manipulation, and arithmetic operations (.S2)

- Loading/storing and arithmetic operations (.D2)

- All data (not program) transfers go through .DI and .D2

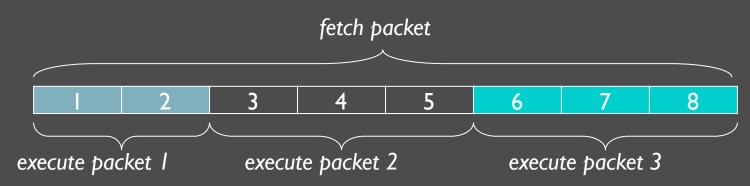

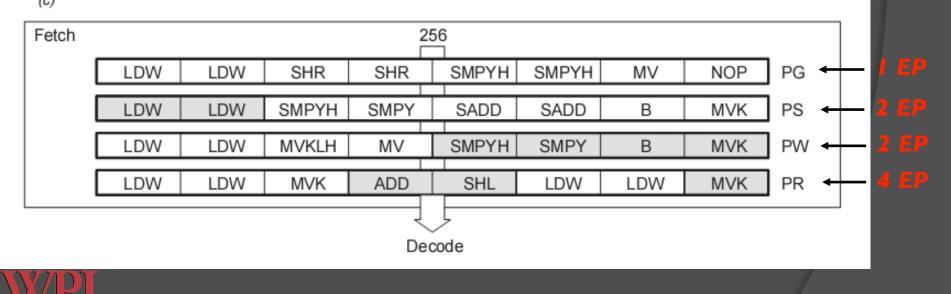

### Fetch & Execute Packets

- C6713 fetches 8 instructions at a time (256 bits)

- <u>Definition</u>: "Fetch packet" is a group of 8 instructions fetched at once.

- Coincidentally, C6713 has 8 functional units.

- Ideally, all 8 instructions are executed in parallel.

- Often this isn't possible, e.g.:

- 3 multiplies (only two .M functional units)

- Results of instruction 3 needed by instruction 4 (must wait for 3 to complete)

### **Execute Packets**

<u>Definition:</u>"Execute Packet" is a group of (8 or less) consecutive instructions in one fetch packet that can be executed in parallel.

- C compiler provides a flag to indicate which instructions should be run in parallel.

- You have to do this <u>manually</u> in Assembly using the double-pipe symbol "||".

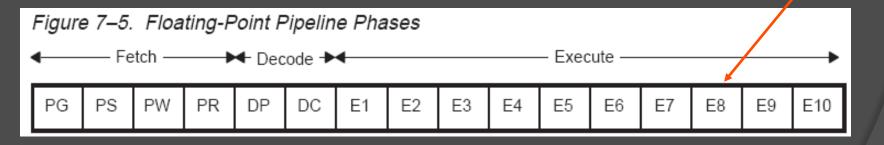

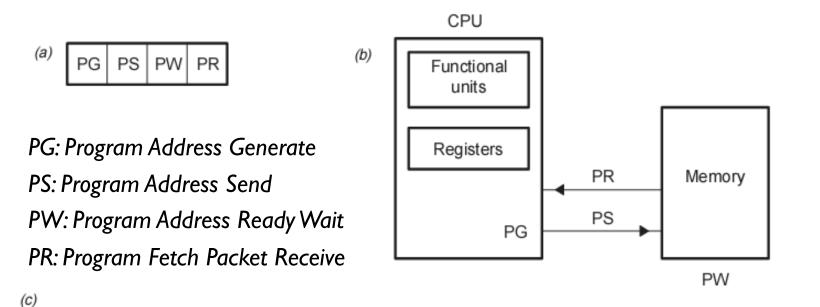

### C6713 Instruction Pipeline Overview

All instructions flow through the following steps:

#### I. Fetch

- a) PG: Program address Generate

- b) PS: Program address Send

- c) PW: Program address ready Wait

- d) PR: Program fetch packet Receive

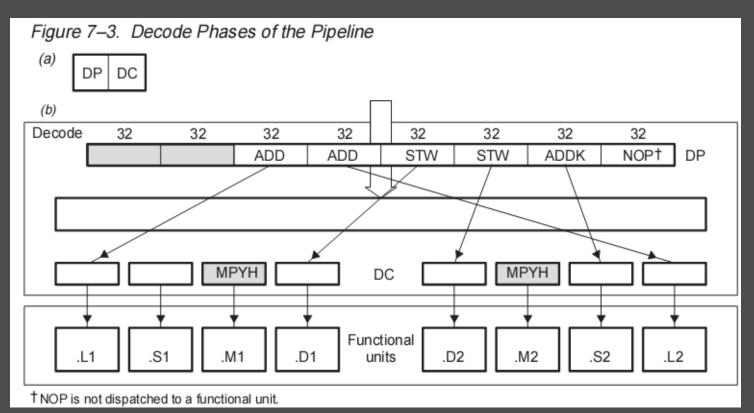

- 2. Decode

- a) DP: Instruction DisPatch

- b) DC: Instruction DeCode

- 3. Execute

- a) 10 phases labeled EI-EI0

- b) Fixed point processors have only 5 phases (E1-E5)

## Pipelining: Ideal Operation

|                 |    |    |    |    |    |    | C  | ock c | ycle |    |    |    |    |    |    |     |     |

|-----------------|----|----|----|----|----|----|----|-------|------|----|----|----|----|----|----|-----|-----|

| Fetch<br>packet | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8     | 9    | 10 | 11 | 12 | 13 | 14 | 15 | 16  | 17  |

| n               | PG | PS | PW | PR | DP | DC | E1 | E2    | E3   | E4 | E5 | E6 | E7 | E8 | E9 | E10 |     |

| n+1             |    | PG | PS | PW | PR | DP | DC | E1    | E2   | E3 | E4 | E5 | E6 | E7 | E8 | E9  | E10 |

| n+2             |    |    | PG | PS | PW | PR | DP | DC    | E1   | E2 | E3 | E4 | E5 | E6 | E7 | E8  | E9  |

| n+3             |    |    |    | PG | PS | PW | PR | DP    | DC   | E1 | E2 | E3 | E4 | E5 | E6 | E7  | E8  |

| n+4             |    |    |    |    | PG | PS | PW | PR    | DP   | DC | E1 | E2 | E3 | E4 | E5 | E6  | E7  |

| n+5             |    |    |    | '  |    | PG | PS | PW    | PR   | DP | DC | E1 | E2 | E3 | E4 | E5  | E6  |

| n+6             |    |    |    |    |    |    | PG | PS    | PW   | PR | DP | DC | E1 | E2 | E3 | E4  | E5  |

| n+7             |    |    |    |    |    |    |    | PG    | PS   | PW | PR | DP | DC | E1 | E2 | E3  | E4  |

| n+8             |    |    |    |    |    |    |    |       | PG   | PS | PW | PR | DP | DC | E1 | E2  | E3  |

| n+9             |    |    |    |    |    |    |    |       |      | PG | PS | PW | PR | DP | DC | E1  | E2  |

| n+10            |    |    |    |    |    |    |    |       |      |    | PG | PS | PW | PR | DP | DC  | E1  |

#### **Remarks:**

• At clock cycle 11, the pipeline is "full"

• There are no holes ("bubbles") in the pipeline in this example

## Pipelining: "Actual" Operation

|                         |                           |    |    |    |    |    | Clo  | ock cy | /cle |    |    |    |    |    |    |    |     |     |

|-------------------------|---------------------------|----|----|----|----|----|------|--------|------|----|----|----|----|----|----|----|-----|-----|

| Fetch<br>packet<br>(FP) | Execute<br>packet<br>(EP) | 1  | 2  | 3  | 4  | 5  | 6    | 7      | 8    | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16  | 17  |

| n                       | k                         | PG | PS | PW | PR | DP | DC   | E1     | E2   | E3 | E4 | E5 | E6 | E7 | E8 | E9 | E10 |     |

| n                       | k+1                       |    |    |    |    |    | DP   | DC     | E1   | E2 | E3 | E4 | E5 | E6 | E7 | E8 | E9  | E10 |

| n                       | k+2                       |    |    |    |    |    |      | DP     | DC   | E1 | E2 | E3 | E4 | E5 | E6 | E7 | E8  | E9  |

| n+1                     | k+3                       |    | PG | PS | PW | PR |      |        | DP   | DC | E1 | E2 | E3 | E4 | E5 | E6 | E7  | E8  |

| n+2                     | k+4                       |    |    | PG | PS | PW | Pipe | eline  | PR   | DP | DC | E1 | E2 | E3 | E4 | E5 | E6  | E7  |

| n+3                     | k+5                       |    |    |    | PG | PS | st   | all    | PW   | PR | DP | DC | E1 | E2 | E3 | E4 | E5  | E6  |

| n+4                     | k+6                       |    |    |    |    | PG |      |        | PS   | PW | PR | DP | DC | E1 | E2 | E3 | E4  | E5  |

| n+5                     | k+7                       |    |    |    |    |    |      |        | PG   | PS | PW | PR | DP | DC | E1 | E2 | E3  | E4  |

| n+6                     | k+8                       |    |    |    |    |    |      |        |      | PG | PS | PW | PR | DP | DC | E1 | E2  | E3  |

#### **Remarks:**

- Fetch packet n has 3 execution packets

- All subsequent fetch packets have I execution packet

- Notice the holes/bubbles in the pipeline caused by lack of parallelization

### Fetch Phases of C6713 Pipeline

Figure 7–2. Fetch Phases of the Pipeline

n n

### Decode Phases of C6713 Pipeline

- **DP** (instruction dispatch) phase

- Fetch packets (FPs) are split into execute packets (EPs)

- Instructions in an EP are assigned to appropriate functional units for decoding

- DC (instruction decode) phase: convert instruction to microcode for appropriate functional unit

#### Execute Phases of C6713 Pipeline

### Execute Phases of C6713 Pipeline

#### • C67x has 10 execute phases (floating point)

| F | Figure 7–5. Floating-Point Pipeline Phases |    |    |    |    |    |         |    |    |    |    |    |    |    |    |     |

|---|--------------------------------------------|----|----|----|----|----|---------|----|----|----|----|----|----|----|----|-----|

|   | ← Fetch ← Decode ►                         |    |    |    |    |    | Execute |    |    |    |    |    |    |    |    |     |

|   | PG                                         | PS | PW | PR | DP | DC | E1      | E2 | E3 | E4 | E5 | E6 | E7 | E8 | E9 | E10 |

- C62x/C64x have 5 execute phases (fixed point)

- Different types of instructions require different numbers of execute phases to complete

- Anywhere between I and all 10 phases

- Most instruction tie up their functional unit for only one phase (EI)

### Execute Stage: Delay Slots

- O How long must we wait for the result of an instruction?

- Most instructions' results are available at the end of EI (called "single-cycle" instructions)

- Examples:

- ABSSP (single precision absolute value)

- RCPSP (single precision reciprocal approximation)

- Some instructions take more time to produce results

- Examples:

- MPYSP (single precision multiply): Results available at the end of E4 (3 delays slots)

- ADDSP (single precision addition): Results available at the end of E4 (3 delay slots)

### Execute Stage: Functional Latency

- How long must we wait for the functional unit to be free?

- Most instructions tie up the functional unit for only one pipeline stage (EI)

- Examples:

- All single-cycle instructions

- Most multicycle instructions, including, for example, ADDSP (single precision addition)

- Some instructions tie up the execution unit for more than one pipeline stage

- Examples:

- MPYDP (double precision multiply): .M execution unit is tied up for 4 pipeline stages (EI-E4). Can't use this functional unit until E4 completes.

### Execution Stage Examples (I)

| ABSSP            | Single-Precision Flo                                 | oating-Point | Absolute Value   |                                                |          |

|------------------|------------------------------------------------------|--------------|------------------|------------------------------------------------|----------|

|                  | ABSSP (.unit) <i>src2</i> , a<br>.unit = . S1 or .S2 | lst          |                  |                                                |          |

|                  | Opcode map field use                                 | ed           | For operand type | Unit                                           |          |

|                  | src2<br>dst                                          |              | xsp<br>sp        | .S1, .S2                                       |          |

|                  |                                                      |              |                  | results available after<br>delay slots)        | El (zero |

| Pipeline         | Pipeline<br>Stage                                    | E1           |                  |                                                |          |

|                  | Read                                                 | src2         |                  |                                                |          |

|                  | Written                                              | dst          |                  | Functional unit free a (1 functional unit late |          |

|                  | Unit in use                                          | .S           | -                | , -                                            |          |

| Instruction Type | Single-cycle                                         |              |                  |                                                |          |

## Execution Stage Examples (2)

| ADDSP                      | Single-Preci                     | Single-Precision Floating-Point Addition |                   |    |                               |  |  |  |

|----------------------------|----------------------------------|------------------------------------------|-------------------|----|-------------------------------|--|--|--|

| Syntax                     | ADDSP (.unit<br>.unit = .L1 or . | ) src1, src2, ds<br>.L2                  | st                |    |                               |  |  |  |

| Pipeline                   | Pipeline<br>Stage                | E1                                       | E2                | E3 | E4                            |  |  |  |

|                            | Read                             | src1<br>src2                             |                   |    |                               |  |  |  |

|                            | Written                          |                                          |                   |    | dst                           |  |  |  |

|                            | Unit in use                      | .L                                       |                   |    |                               |  |  |  |

| Instruction Type           | 4-cycle                          |                                          |                   |    | vailable after<br>elay slots) |  |  |  |

| Delay Slots                | 3                                | Functional u                             | nit free after El | Υ. | •                             |  |  |  |

| Functional Unit<br>Latency | 1                                |                                          | Il unit latency)  |    |                               |  |  |  |

## Execution Stage Examples (3)

| MPYSP                      | Single-Precisio              | n Floating                            | g-Point Multiply                                                                           |                                  |                   |

|----------------------------|------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------|-------------------|

| Syntax                     | MPYSP (.unit) si             | rc1, src2, d                          | dst                                                                                        |                                  |                   |

|                            | .unit = .M1 or .M            | 2                                     |                                                                                            |                                  |                   |

| Pipeline                   | Pipeline<br>Stage            | E1                                    | E2                                                                                         | E3                               | E4                |

|                            | Read                         | src1<br>src2                          |                                                                                            |                                  |                   |

|                            | Written                      |                                       |                                                                                            |                                  | dst               |

|                            | Unit in use                  | .M                                    |                                                                                            |                                  |                   |

|                            | CMPGTDP, MPY reduced by one, | <b>DP</b> , or <b>SU</b><br>because f | burce for the ADI<br>BDP instruction, th<br>these instructions is<br>the upper word of the | e number of de<br>read the lower | elay slots can be |

| Instruction Type           | 4-cycle                      |                                       |                                                                                            | s available af                   | fter              |

| Delay Slots                | 3                            |                                       | Υ.                                                                                         | delay slots)                     | E1                |

| Functional Unit<br>Latency | 1                            |                                       |                                                                                            | nit free after<br>I unit latency |                   |

### Execution Stage Examples (4)

| MPYDP                      | Double-Pre                                                                 | cision I           | Floating                    | g-Point                       | t Multip               | ly                         |                      |                  |                        |                     |        |

|----------------------------|----------------------------------------------------------------------------|--------------------|-----------------------------|-------------------------------|------------------------|----------------------------|----------------------|------------------|------------------------|---------------------|--------|

| Syntax                     | MPYDP (.uni                                                                | it) <i>src1</i> ,  | src2, d                     | st                            |                        |                            |                      |                  |                        |                     |        |

|                            | .unit = .M1 or                                                             | r .M2              |                             |                               |                        |                            |                      |                  |                        |                     |        |

| Pipeline                   | Pipeline<br>Stage                                                          | E1                 | E2                          | E3                            | E4                     | E5                         | E6                   | E7               | E8                     | E9                  | E10    |

|                            | Read                                                                       |                    | src1_l<br>src2_h            |                               |                        |                            |                      |                  |                        |                     |        |

|                            | Written                                                                    |                    |                             |                               |                        |                            |                      |                  |                        | dst_l               | dst_h  |

|                            | Unit in use                                                                | .М                 | .М.                         | .М.                           | .М.                    |                            |                      |                  |                        |                     |        |

|                            | If <i>dst</i> is use<br><b>CMPGTDP</b> , N<br>reduced by c<br>source one c | MPYDP,<br>one, bea | , or <b>SUE</b><br>cause th | BDP ins<br>hese in<br>e upper | struction<br>struction | n, the<br>ns re<br>f the l | num<br>ad th<br>DP s | iber o<br>he lov | of dela<br>wer w<br>e. | ay slots<br>vord of | can be |

| Instruction Type           | MPYDP                                                                      |                    |                             |                               | lay slot               |                            |                      | 1001             |                        | (*                  |        |

| Delay Slots                | 9                                                                          |                    | Functio                     |                               | ,<br>hit free (        | ·                          | <sup>-</sup> E4      |                  |                        |                     |        |

| Functional Unit<br>Latency | 4                                                                          |                    |                             |                               | unit lat               | •                          |                      |                  |                        |                     |        |

|                            |                                                                            |                    |                             |                               |                        |                            |                      |                  |                        |                     |        |

- IMPORTANT: Delay slots are not the same as functional unit latency

- Example:

MPYSP .MI AI,A2,A3 MPYSP .MI A4,A5,A6 MPYSP .MI A7,A8,A9 MPYSP .MI AI0,AII,AI2 ;A3 = A1 × A2 ;A6 = A4 × A5 ;A9 = A6 × A7 ;A12 = A10 × A11

Is this code ok?

• What about this code?

MPYSP .MI AI,A2,A3 MPYSP .MI A3,A4,A5

;A3 = A1 × A2 ;A5 = A3 × A4

- You are probably going to get strange results here because the result in A3 is not available until E4 completes for the first MPYSP instruction

- "Data hazard" due to the delay slots in MPYSP

- How to "fix" the last example

| MPYSP .MIAI,A2,A3  | $;A3 = AI \times A2$                  |

|--------------------|---------------------------------------|

| NOP 3              | ; insert 3 delay slots                |

|                    | ; results of first multiply now in A3 |

| MPYSP .MI A3,A4,A5 | ;A5 = A3 x A4                         |

• What about this code?

#### MPYDP .MI AI:A0,A3:A2,A5:A4 MPYDP .MI A7:A6,A9:A8,A11:A10

- This won't work because the functional unit MI is tied up for 4 clock cycles (EI-E4) by MPYDP

- "Resource conflict" due to the functional latency in MPYDP

- How to fix it: MPYDP .MI AI:A0,A3:A2,A5:A4

NOP 3 ; 3 NOPs for func latency MPYDP .MI A7:A6,A9:A8,A11:A10

• What about this code?

#### MPYDP .MI AI:A0,A3:A2,A5:A4 MPYDP .MI A5:A4,A8:A7,A11:A10

#### Two problems now!

- Resource conflict for .MI unit (E2-E4)

- Data hazard for result in A5:A4 (E2-E10)

- The "fix":

MPYDP .MI AI:A0, A3:A2, A5:A4

NOP 9

MPYDP .MI A5:A4, A8:A7, A11:A10

Note: Could use MI after E4, but A5:A4 not available until after E10.

#### Functional Latency & Delay Slots

- Sumplement of the functional unit to be free?

- Oblay Slots: How long must we wait for the result of a calculation to be available?

- General remarks:

- Functional unit latency <= Delay slots</li>

- Strange results will occur in ASM code if you don't pay attention to delay slots and functional unit latency

- All problems can be resolved by "waiting" with NOPs

- <u>Efficient ASM code tries to keep functional units busy all</u> of the time.

- Efficient code is hard to write (and follow).

#### Additional Constraints: Data Cross-Paths

• TMS320C6x core has A side and B side

- A side: MI, SI, LI, DI, and register file A0-A15

- B side: M2, S2, L2, D2, and register file B0-B15

- Cross path instruction examples:

- MPYSP .MIx A2, B2, A4 ; cross path brings B2 to MI

- MPYSP .M2x A2, B2, B4 ; cross path brings A2 to M2

- Constraint: Only two cross-paths are available per cycle:  $A \rightarrow 2$  and  $B \rightarrow I$ .

- Note: Can't have two A→2 or two B→1 cross paths in the same cycle.

### Additional Constraints

#### Memory constraints

- Two memory accesses can be performed in one cycle if they don't access the same bank of memory

- See TMS320C6000 Programmer's Guide

#### Load/Store constraints

- Address register must agree with .D unit, e.g.:

LDW .DI \*AI,A2 ; valid because AI and DI agree

- Parallel loads and stores must use different register files

- See TMS320C6000 Programmer's Guide

## Suggested Reading

- Reference material (on course web page)

- TMS320C6000 CPU Instruction Set and Reference Guide

- TMS320C6000 Programmer's Guide

- Kehtarnavaz Chap 3

- Kehtarnavaz Chap 7

- Chassaing has some ASM example code in the myproject directory (see, for example, FIRcASM.pjt)